|

|||

| HSG |

|

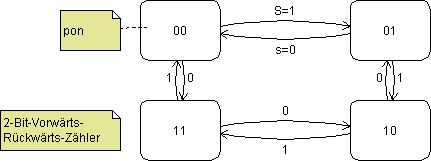

Systematische Entwicklung eines 2-Bit-Zählers

1.Zustandsdiagramm

s=1: vorwärts

s=0: rückwärts

2.Übergangsschaltnetzs z1 z0 z1' z0' ------------------ 0 0 0 1 1 0 0 1 0 0 0 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 1 1 1 1 0 0 Eingabe im Programm QMC (leider nur für Windows):

|

3.Minimierung1-Zeilen für z1' 000 011 101 110 1-Zeilen für z0' 000 010 100 110 Der Quine-McCluskey-Optimierer liefert: ~a & ~b & ~c v a & b & ~c v a & ~b & c v ~a & b & c = /s*/z1*/z0 + s*z1*/z0 + s*/z1*z0 + /s*z1*z0 ~c = /z0 Ausgabe vom Programm QMC:

|