|

|||

| HSG |

|

Master-Slave-FlipFlop aus zwei Daten-FlipFlops und einem Inverter

Schaltskizze zu den Daten-FlipFlops

Material zum ehemaligen Hardware-Praktikum der Universität Kaiserslautern

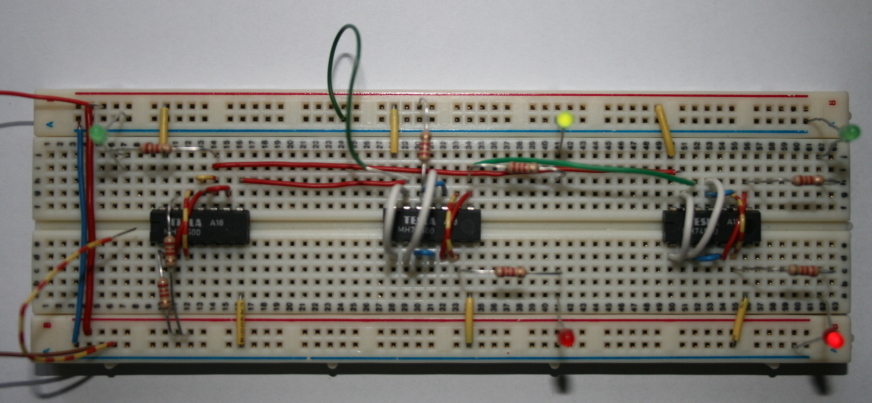

Aufbau eines taktzustandgesteuerten Daten-FlipFlop

Achtung: Bei CMOS-Gattern müssen unbenutzte Eingänge fest auf Null oder Eins gelegt werden.

Das Datenblatt zum Baustein 4011

1.Schritt

Es wird anhand des Schaltplans und des Datenblatts ein Aufbauplan mit

Pin-Nummern skizziert. 4011.pdf

4011.pdf

2.Schritt

Die Stromversorgung wird gelegt. Rot wird für +4,5V, blau (oder schwarz) für -.

Der Übersichtlichkeit halber wird + auf der einen Seite und - auf der anderen Seite

des Boards bereitgestellt. Kleine Brücken ergeben mehr Anschlussmöglichkeiten.

Die Spannung wird erst am Schluss angelegt.

Die Stromversorgung wird gelegt. Rot wird für +4,5V, blau (oder schwarz) für -.

Der Übersichtlichkeit halber wird + auf der einen Seite und - auf der anderen Seite

des Boards bereitgestellt. Kleine Brücken ergeben mehr Anschlussmöglichkeiten.

Die Spannung wird erst am Schluss angelegt.

3.Schritt

Es empfiehlt sich beim Aufbau eine gewisse Systematik einzuhalten. Hier wird der

Aufbauplan von links nach rechts abgearbeitet. Die beiden 3,3kOhm-Widerstände von

13 und 9 nach + werden eingebaut.

Es empfiehlt sich beim Aufbau eine gewisse Systematik einzuhalten. Hier wird der

Aufbauplan von links nach rechts abgearbeitet. Die beiden 3,3kOhm-Widerstände von

13 und 9 nach + werden eingebaut.

4.Schritt

Es folgen die Verbindungen 9-12, 8-11, 1-11 und 6-10.

Es folgen die Verbindungen 9-12, 8-11, 1-11 und 6-10.

5.Schritt

Die Verbindungen 2-4 und 3-5 werden eingebaut.

Die Drähte können - wie hier - auch etwas kürzer gehalten werden.

Die Verbindungen 2-4 und 3-5 werden eingebaut.

Die Drähte können - wie hier - auch etwas kürzer gehalten werden.

6.Schritt

Jetzt werden die Anzeigeelemente aufgebaut. Die LEDs werden mit dem Pluspol

(Anschlussdraht ist etwas länger) nach links eingesteckt. Die

Verbindungen zu 3 und 4 werden gesteckt. Zum Schluss werden die 1kOhm-Widerstände

nach Masse (-) hin eingebaut.

Jetzt werden die Anzeigeelemente aufgebaut. Die LEDs werden mit dem Pluspol

(Anschlussdraht ist etwas länger) nach links eingesteckt. Die

Verbindungen zu 3 und 4 werden gesteckt. Zum Schluss werden die 1kOhm-Widerstände

nach Masse (-) hin eingebaut.

7.Schritt

Dateneingang 13 und Takteingang 9 sind über die Widerstände zunächst immer

an einer logischen 1. Sie werden mit Masse (-) verbunden, wenn man eine

logische 0 am Eingang haben will. Achtung, die richtige Seite der Widerstände

verbinden, sonst wird durch einen Kurzschluss die Batterie auf der Stelle

entleert. Die "Eingabeleitungen" sind hier grün.

Dateneingang 13 und Takteingang 9 sind über die Widerstände zunächst immer

an einer logischen 1. Sie werden mit Masse (-) verbunden, wenn man eine

logische 0 am Eingang haben will. Achtung, die richtige Seite der Widerstände

verbinden, sonst wird durch einen Kurzschluss die Batterie auf der Stelle

entleert. Die "Eingabeleitungen" sind hier grün.

Um die Schaltung testen zu können, wird nun die Versorgungsspannung

angelegt. Liegt der Dateneingang 13 auf 1, so leuchtet die grüne Led, das

FlipFlop ist gesetzt.

8.Schritt

Solange der Takteingang 9 auf logisch 1 liegt, ist das FlipFlop transparent.

Dem entsprechend kippt es - wie im Bild - wenn der Dateneingang auf 0 gelegt

wird.

Solange der Takteingang 9 auf logisch 1 liegt, ist das FlipFlop transparent.

Dem entsprechend kippt es - wie im Bild - wenn der Dateneingang auf 0 gelegt

wird.

9.Schritt

Der Takteingang 9 auf wird auf logisch 0 gelegt, das FlipFlop ist gesperrt.

Änderungen am Dateneingang 13 bewirken keine Zustandsänderung

Der Takteingang 9 auf wird auf logisch 0 gelegt, das FlipFlop ist gesperrt.

Änderungen am Dateneingang 13 bewirken keine Zustandsänderung

Aufgabe

Speichere eine jeweils eine 0 und eine 1 ein und beobachte das beschriebene Verhalten.

Links

- Webquest - wikipedia

- Steckplatine - wikipedia

- Transistor-Transistor-Logik - wikipedia

- LED - wikipedia

- Widerstände - www.elektronik-kompendium.de

- Farbcode - www.elektronik-kompendium.de

- LED - www.elektronik-kompendium.de

- 7400.pdf

- Schaltzeichen in der Digitaltechnik - www.elektronik-kompendium.de

- TTL-Code - www.elektronik-kompendium.de

- Veranschaulichungen

- virtuelles Steckboard

- fritzing.org

- Steckboard - www.reichelt.de

- 75LS00 - www.reichelt.de

- 75HC14 - www.reichelt.de

- 74xx - www.mikrocontroller.net