|

|||

| HSG |

|

Befehle-Modul

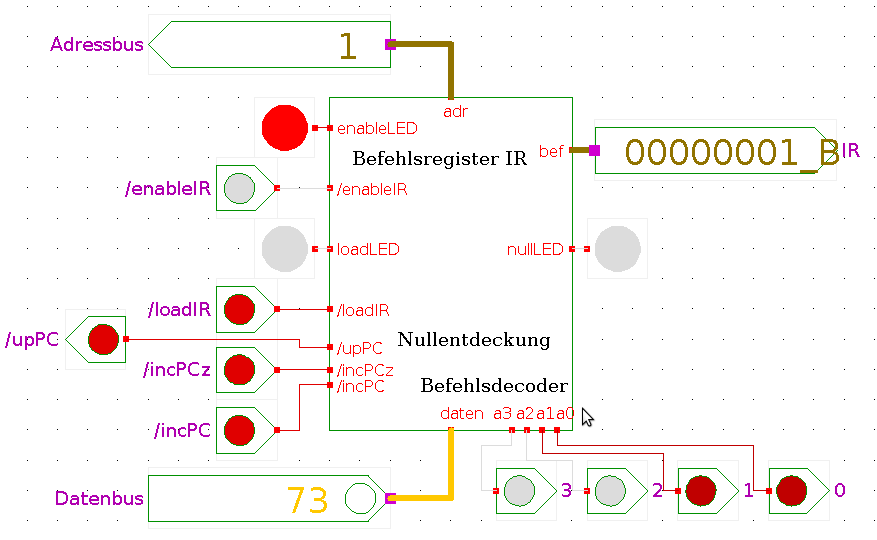

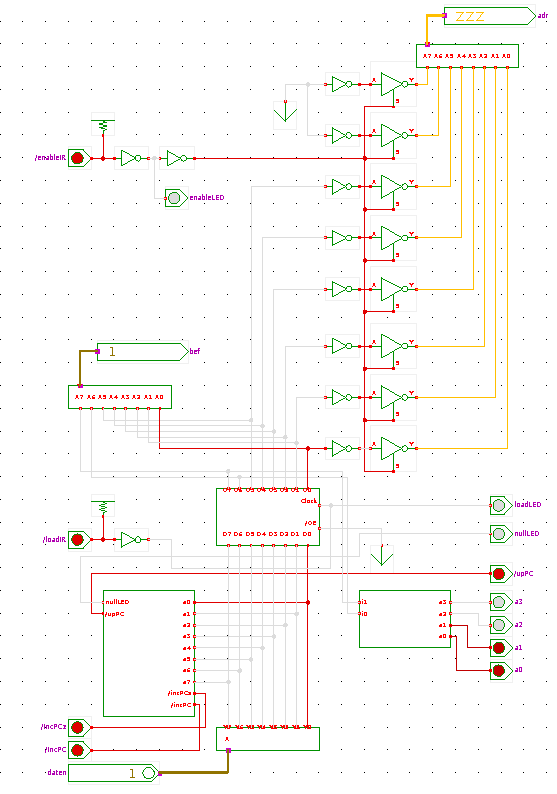

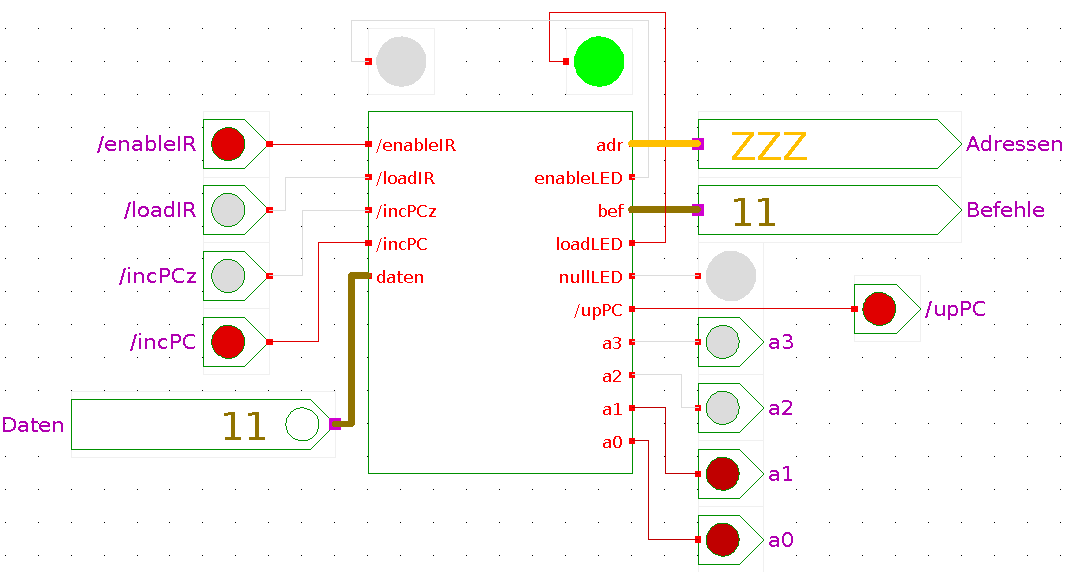

Die Befehle-Platine enthält zunächst das eigentliche Befehlsregister (IR, instruction register). Es kann über die Steuersignale /loadIR und /enableIR zum Laden bzw. Schreiben gebracht werden. Es ist zu beachten, dass nur die 6 unteren Bits die Adresse bilden.

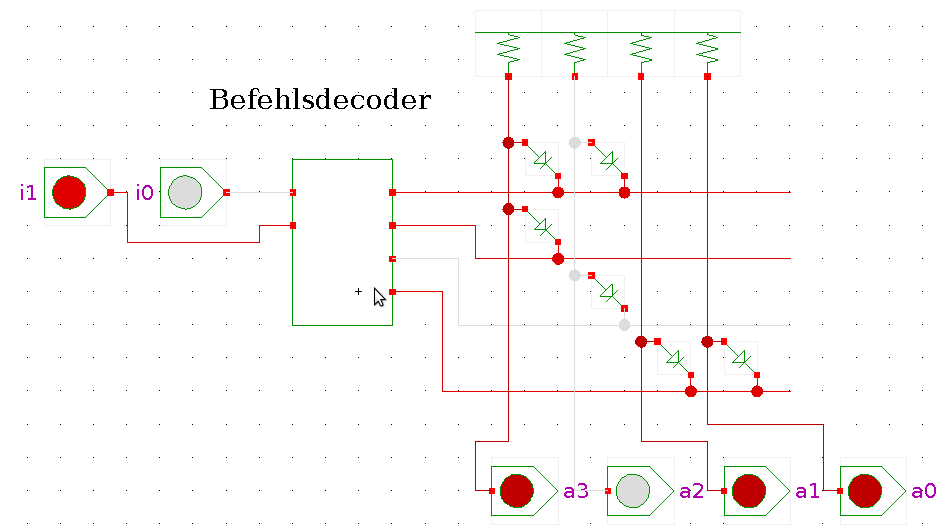

Die obersten 2 Bit eines Befehls enthalten den sogenannten Opcode. Sie bestimmen, welcher Befehl ausgeführt werden soll. Für jeden Befehl ist im Steuerwerk sein Mikrocode abgelegt. Der Befehlsdecoder berechnet aus dem Opcode die richtige Einsprungadresse im Mikroprogramm.

Befehl opcode Einsprungadresse -------------------------------- inc 00 0011 3 dec 01 0111 7 jmp 10 1011 11 tst 11 1100 12

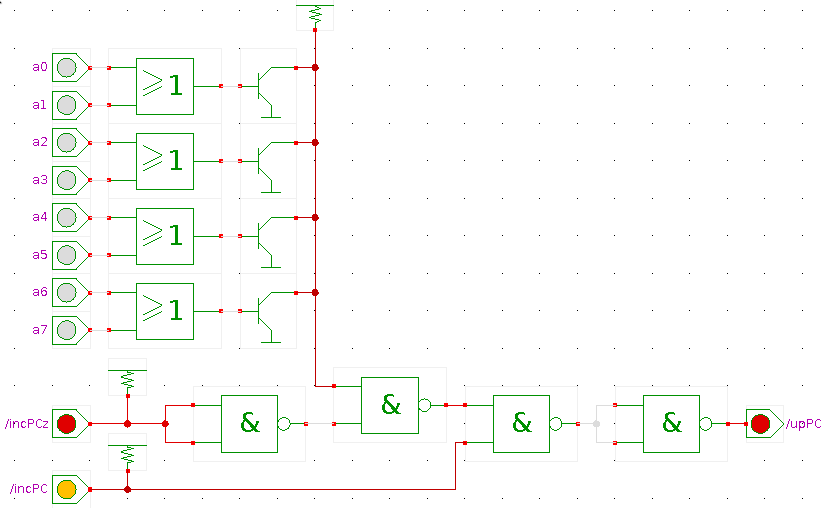

Die Nullentdeckungslogik beobachtet den Datenbus und erkennt, wenn dort eine Null anliegt. Sie reicht das Signal /incPC (PC unbedingt erhöhen) unabhängig vom Businhalt weiter. Das Signal /incPCz (PC erhöhen, wenn am Bus Null anliegt) wird nur weitergegeben, wenn am Bus Null anliegt. Dabei ist zu bedenken, dass das Signal /incPC mit der steigenden Flanke wirksam wird.

Aufgabe

Starte die Simulation zum Befehle-Modul und vollziehe das beschriebene Verhalten nach.

Es folgen Details, die zunächst übergangen werden können.

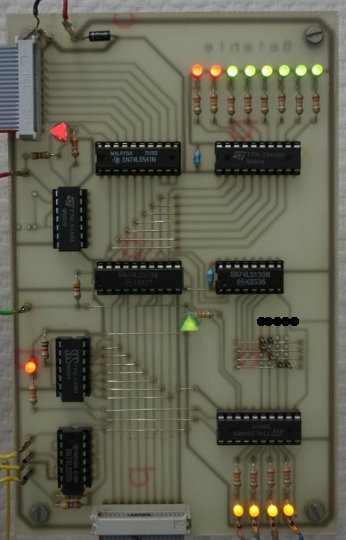

Befehle-Platine

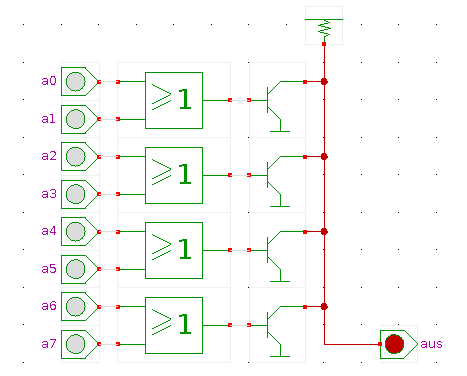

Nullentdeckungslogik

Die Nullentdeckung verwendet 4 Nor-Gatter mit offenem Kollektorausgang 74LS33 und einen Pull-Up-Widerstand.

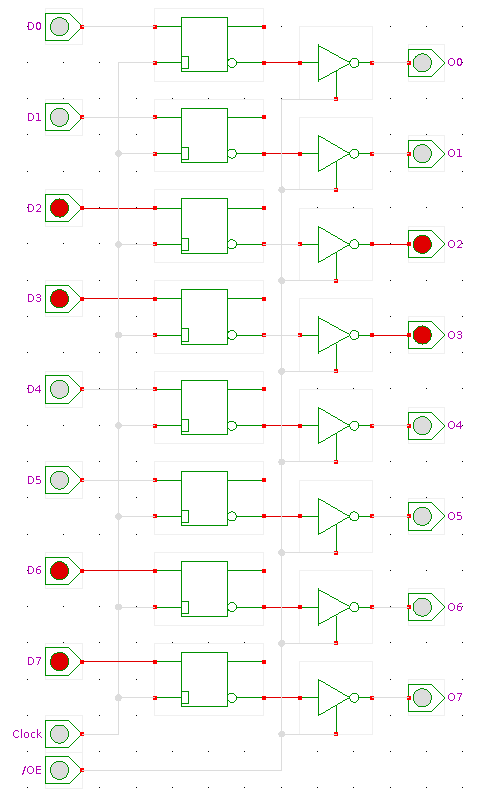

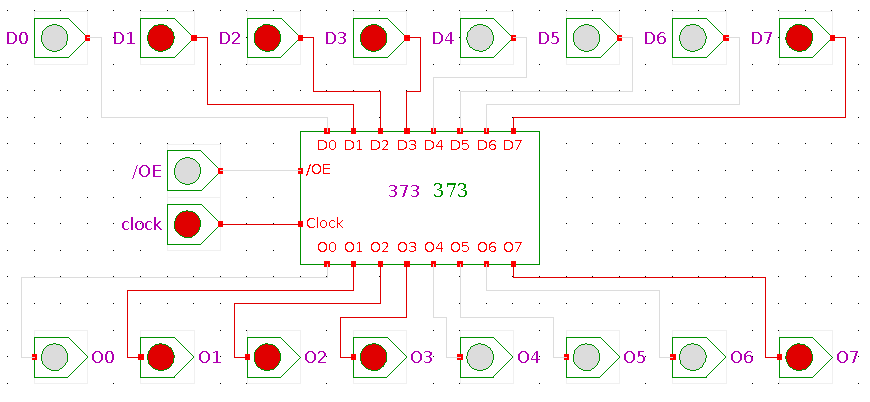

8-fach transparentes Latch

Test von 74LS373

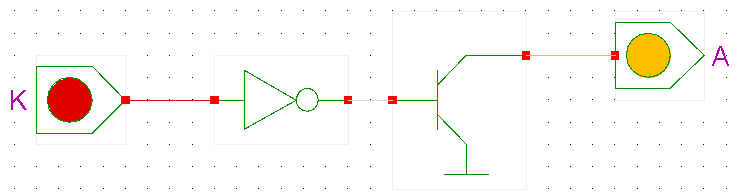

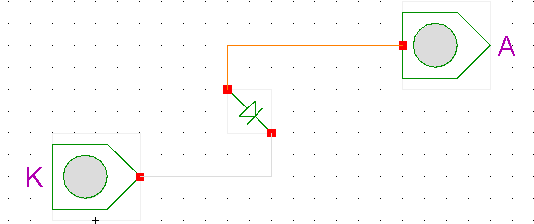

Diode

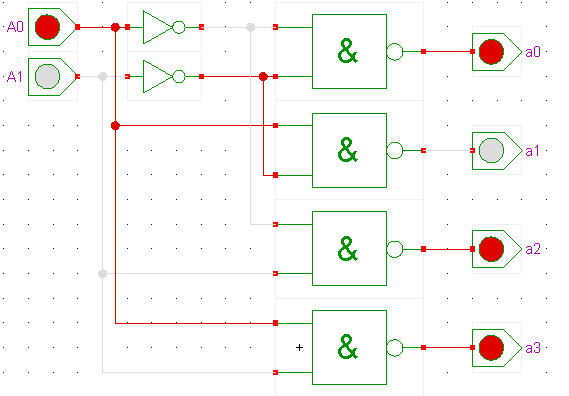

1-aus-4-Decoder

Befehlsdecoder

Aufgabe

Entwickele durch 'Einlöten' der Dioden in decoder.hds eine Schaltung, die folgender Wahrheitstabelle genügt.

i1 i0 | o3 o2 o1 o0 ------+------------ 0 0 | 1 0 0 1 0 1 | 0 1 0 1 1 0 | 1 1 0 0 1 1 | 0 0 1 1

Test des Befehle-Makros

Links

- PLA-Demo - Hades

- Befehle-Modul - Bonsai-Computer

- Wired-AND bus - Hades

- 74LS373